台积电推出的新型封装技术备受关注,它适用于对性能有高要求的应用场景。这使得芯片设计师能够制造出体积更小、性能更强的处理器。这项技术亮点众多,值得细细品味。

CoWoS技术原理与优势

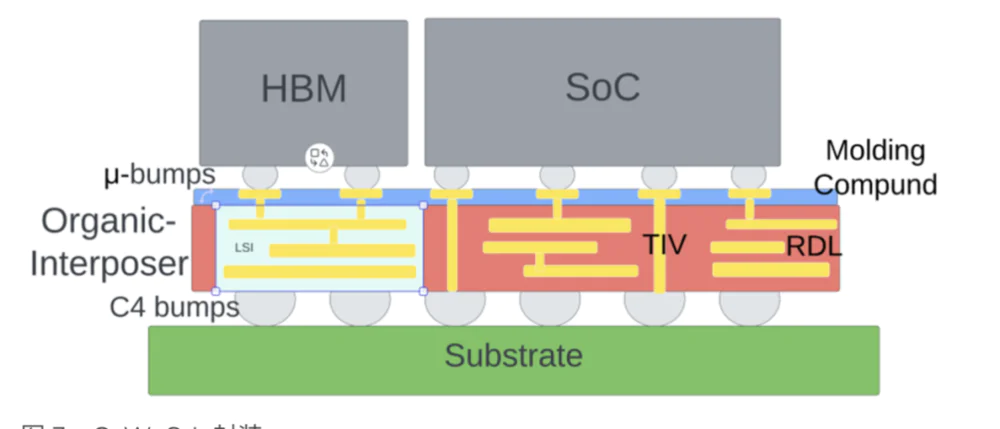

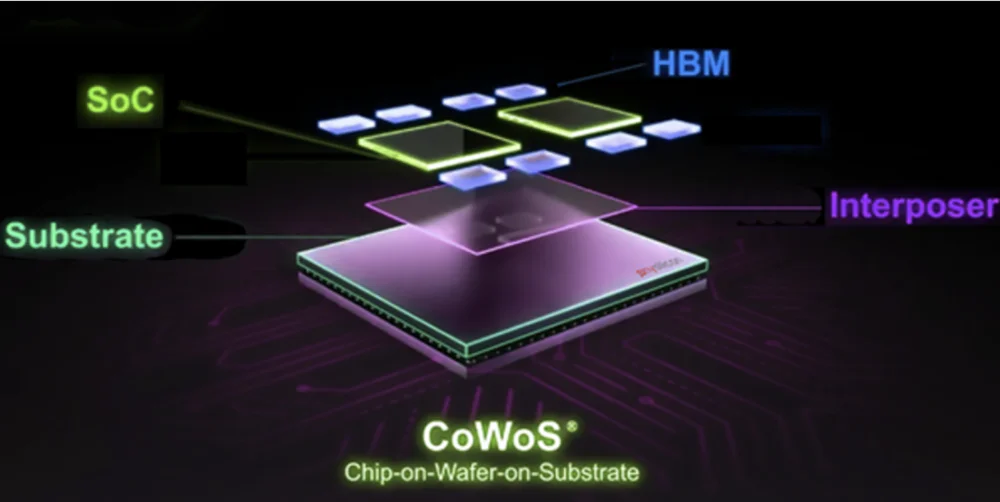

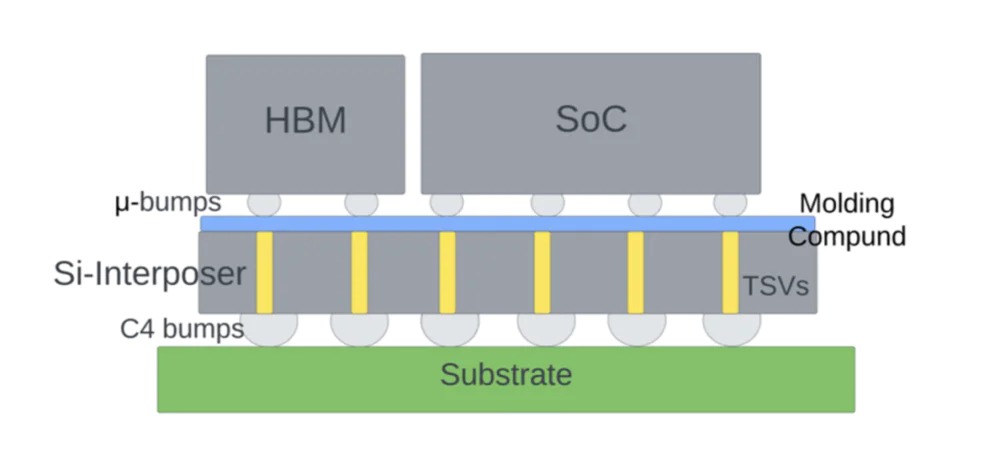

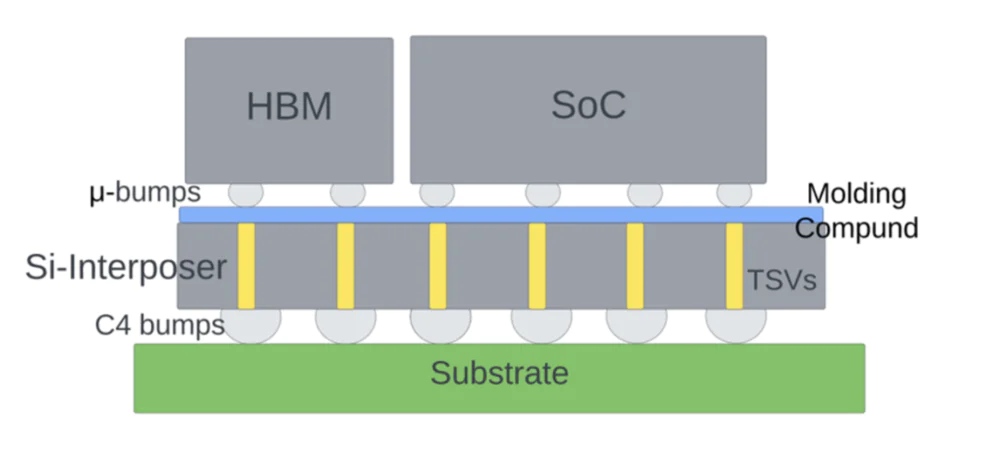

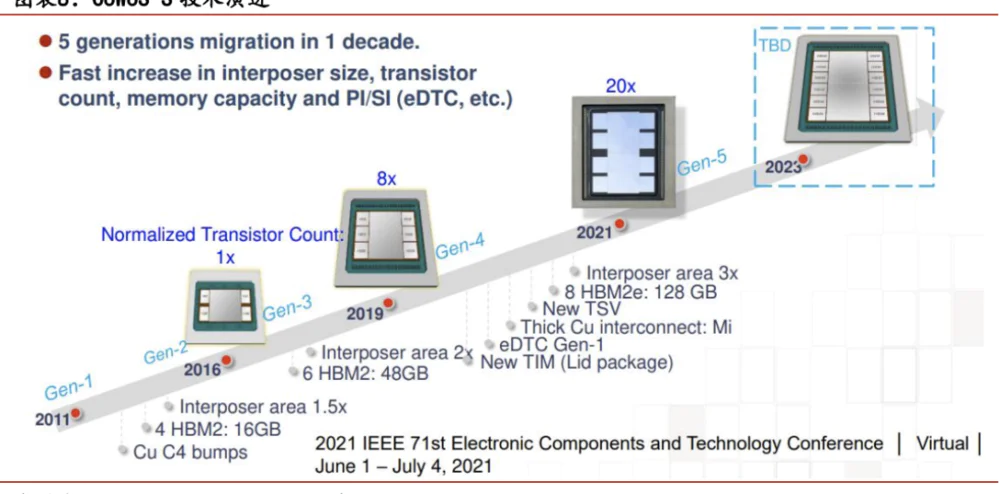

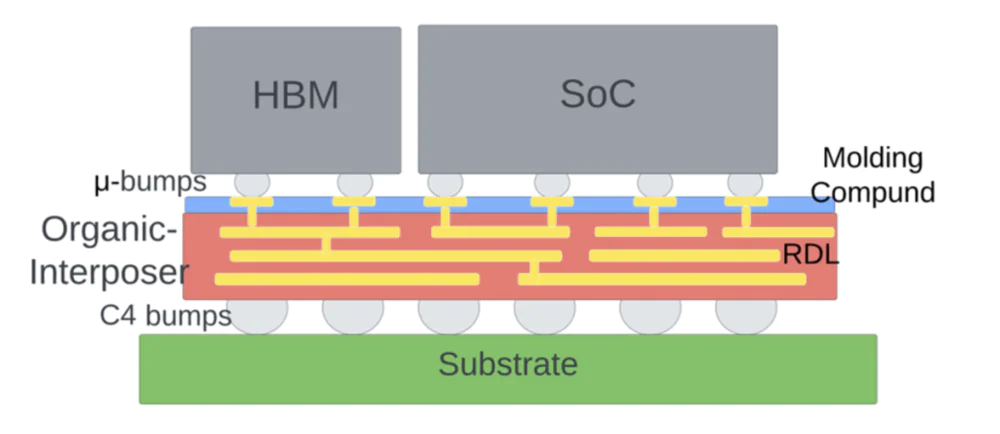

CoWoS技术属于高端封装领域。它采用2.5D水平叠加和3D垂直叠加设计,颠覆了传统封装方式。比如,它能将GPU和HBM完美结合。此外,它提供了更多的I/O接口,且在尺寸和成本上更具优势。在实际使用中,可以在中介层放置多个芯片,实现高效的连接与通信。与传统的封装技术相比,它在晶体管支持量上远超SiP等旧技术。

传统封装技术以前在PCB上安装多个逻辑SoC较为常见,而CoWoS技术则能在同一中介层和基板上同时容纳多个逻辑SoC与HBM。

极高晶体管密度的可能

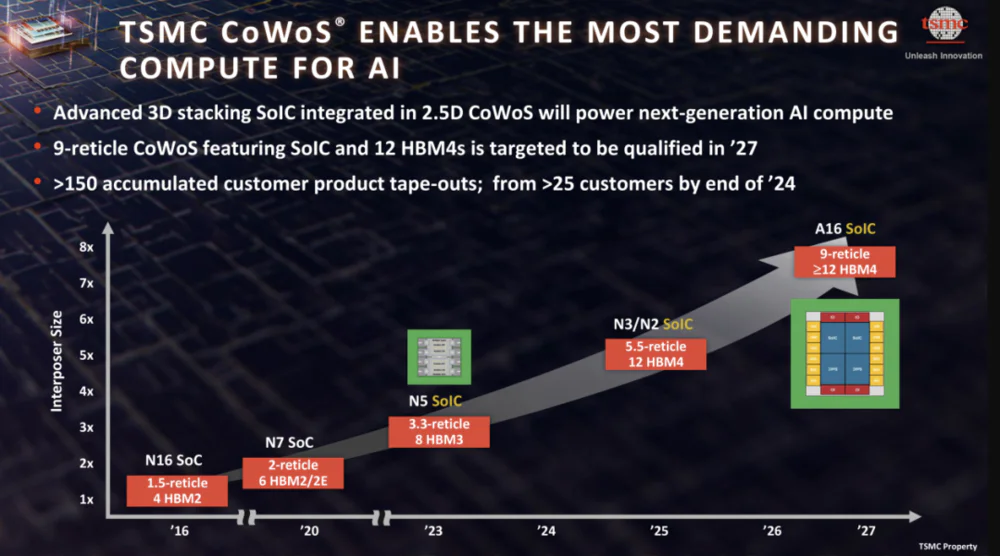

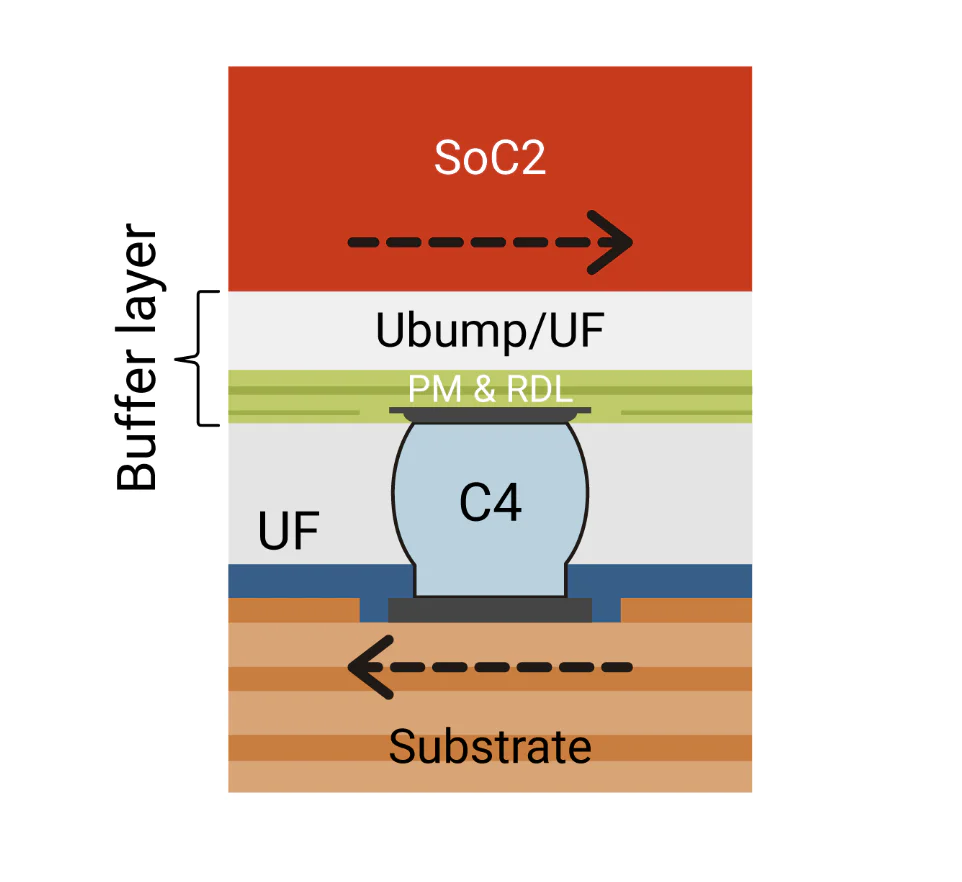

台积电计划利用9光罩CoWoS技术,将1.6nm芯片放置在2nm芯片之上。这种堆叠技术能显著提高晶体管密度。晶体管密度的提升对性能提升至关重要。晶体管数量的增加通常会导致性能的显著增强。这与2.5D和3D集成技术的发展方向相似,追求高晶体管密度的集成技术,能使芯片在相同面积内具备更强的计算能力。

热管理能力的提升

CoWoS技术中,硅和有机中介层有效提升了堆叠集成电路的热控制能力。台积电还推出了MetalTim散热方案,相较于第一代GelTIM,封装热阻显著下降。这就像为高性能芯片营造了更优的散热条件,确保芯片能稳定运行。这种热管理技术确保了高性能芯片在高运算频率下能稳定工作,防止因过热而引起运算错误或性能降低。

尺寸和成本的降低

CoWoS技术能缩小体积并降低成本。在同一层和底板上,可以安装多个逻辑SoC和HBM,从而减少整体成本。与过去传统封装技术相比,它需要的连接步骤和组件更少。这对芯片的大规模生产非常有益。比如,对于大规模生产的AI芯片,成本的降低能让更多用户负担得起。此外,小型化设计还让它能应用于更多空间受限的设备中。

制造复杂性和成本挑战

CoWoS技术涉及2.5D和3D集成,其制造过程较为复杂。在晶圆芯片安装前,必须进行单独的测试;安装后,还需进行复测。相较传统技术,对2.5D或3D集成电路的测试难度更大。这无疑提高了成本。企业需在成本增加与性能提升之间权衡利弊。比如,中小型企业可能需在预算有限的情况下,考虑是否采纳这项技术。

电源完整性问题

CoWoS封装适用于性能要求高的应用场景,但遇到了电源稳定性的难题。这种封装有较高的数据转换速度和较低的工作电压。尽管不断进步,确保了产量、功率和热稳定性的提升,通过扩大中介层面积来增加晶圆共基板的数量,但问题依然存在。需要意识到,电源供应的不稳定可能会对芯片的正常运作造成影响。

你认为小型芯片企业如何才能有效应对使用CoWoS技术带来的成本挑战?欢迎大家在评论区留言,为这篇文章点赞并转发。